Highlights:

- Proven flow enhanced with unified placement and physical optimization engines used to complete hundreds of advanced-node tapeouts at 16nm to 5nm and below

- Industry’s first unified physical optimization engine with ML capabilities, offering up to 20% additional PPA improvement versus previous flow

- Only digital full flow with integrated timing and voltage-drop (IR drop) signoff engines, which provides users with unparalleled signoff convergence

SAN JOSE, Calif. — (BUSINESS WIRE) — March 17, 2020 — Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced that the new release of the Cadence® digital full flow—proven with hundreds of completed advanced-node tapeouts—has been enhanced to further optimize power, performance and area (PPA) results across a variety of application areas including automotive, mobile, networking, high-performance computing and artificial intelligence (AI). The flow features multiple industry-first capabilities including unified placement and physical optimization engines plus machine learning (ML) capabilities, enabling design excellence with up to 3X faster throughput and up to 20% improved PPA.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20200317005213/en/

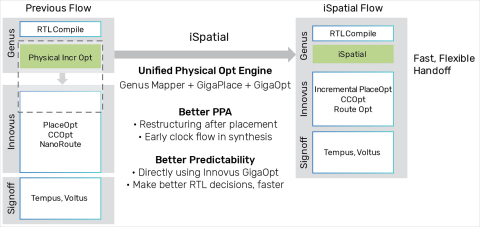

The Cadence digital full flow has been enhanced to further optimize power, performance and area (PPA) results across a variety of application areas including automotive, mobile, networking, high-performance computing and artificial intelligence (AI). (Graphic: Business Wire)

For more information on the Cadence digital full flow, visit www.cadence.com/go/digital.

The new Cadence digital full flow delivers the PPA and throughput benefits through the following key enhancements:

- Cadence digital full flow’s iSpatial technology: The iSpatial technology integrates the Innovus™ Implementation System’s GigaPlace™ Placement Engine and the GigaOpt™ Optimizer into the Genus™ Synthesis Solution, providing techniques such as layer assignment, useful clock skew and via pillars. The iSpatial technology allows a seamless transition from Genus physical synthesis to Innovus implementation using a common user interface and database.

- ML capabilities: ML capabilities enable users to leverage their existing designs to train the iSpatial optimization technology to minimize design margins versus traditional place and route flows.

- Optimal signoff convergence: The digital full flow incorporates unified implementation, timing- and IR-signoff engines, offering enhanced signoff convergence by concurrently closing the design for all physical, timing and reliability targets. This allows customers to reduce design margins and iterations.

“The new digital full flow enhancements build upon the widely adopted integrated flow, further advancing Cadence’s digital and signoff design leadership position and enabling customers to achieve SoC design excellence,” said Dr. Chin-Chi Teng, senior vice president and general manager of the Digital & Signoff Group at Cadence. “We’ve collaborated closely with our customers who are under pressure to meet compressed schedules with increasingly large designs, offering them the features they need to realize PPA gains more efficiently.”

The Cadence digital full flow consists of the Innovus Implementation System, Genus Synthesis Solution, Tempus™ Timing Signoff Solution and Voltus™ IC Power Integrity Solution. It provides customers with a fast path to design closure and better predictability and supports the company’s Intelligent System Design™ strategy, which enables advanced-node system-on-chip (SoC) design excellence.

Customer Endorsements

“We spend a significant effort tuning our high-performance cores to meet our aggressive performance goals. Using the new ML capabilities in the Innovus Implementation System’s GigaOpt Optimizer, we were able to automatically and quickly train a model of our CPU core, which resulted in an improved maximum frequency along with an 80% reduction in total negative slack. This enabled 2X shorter turnaround time for final signoff design closure.”

-Dr. SA Hwang, general manager of Computing and Artificial Intelligence Technology Group at MediaTek

“The Cadence digital full flow with iSpatial technology accurately predicts full placement optimization of PPA and enabled us to achieve 3X faster design turnaround time by quickly iterating on RTL, constraints and floorplan while improving total power by 6%. Furthermore, Cadence’s unique ML capabilities allowed us to train a model of our design on Samsung Foundry's 4nm EUV node, which helped us further achieve a 5% performance improvement and 5% leakage power savings.”

-Jaehong Park, executive vice president of Foundry Design Platform Development at Samsung Electronics

About Cadence

Cadence is a pivotal leader in electronic design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications including consumer, hyperscale computing, 5G communications, automotive, aerospace, industrial and health. For six years in a row, Fortune Magazine has named Cadence one of the 100 Best Companies to Work For. Learn more at www.cadence.com.

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All other trademarks are the property of their respective owners.

View source version on businesswire.com: https://www.businesswire.com/news/home/20200317005213/en/

Contact:

Cadence Newsroom

408-944-7039

newsroom@cadence.com