Henderson, NV. – October 11, 2016 – Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification solutions for system and ASIC designs, will present the spectrum of pre-silicon verification solutions at theDVCon Europe Conference and Exhibition to be held October 19-20, 2016 in Munich, Germany.

At

DVCon Europe, Aldec will demonstrate industry-proven verification methodologies and solutions using a Network-on-Chip (NoC) design based on research conducted at Stanford University by Daniel Ulf Becker. “The NoC was built as a mesh topology with a configurable number of routers that provide device connection nodes,” illustrates Krzysztof Szczur, Aldec Hardware Verification Products Manager. “The network is able to transfer data packets between any pair of nodes and therefore can serve as the backbone of a complex System-on-Chip (SoC) ASIC design.” “Verification of complex designs comprised of NoC structures requires a robust chain of verification methodologies such as static linting, high-performance HDL simulation/debugging, and emulation,” said Louie De Luna, Aldec Director of Marketing. “The Verification Spectrum begins as soon as the first lines of HDL code are available, where designers use static linting to catch common bugs and check code sanity. Then HDL simulation using a UVM Verification environment is completed to achieve the highest level of debugging with Structural and Functional Coverage. Finally, to shorten days or weeks of simulation runs, long test sequences of constrained-random testbenches can be accelerated using an emulator. With Aldec’s 35,000+ user community, Aldec is committed to support every stage of this process.”

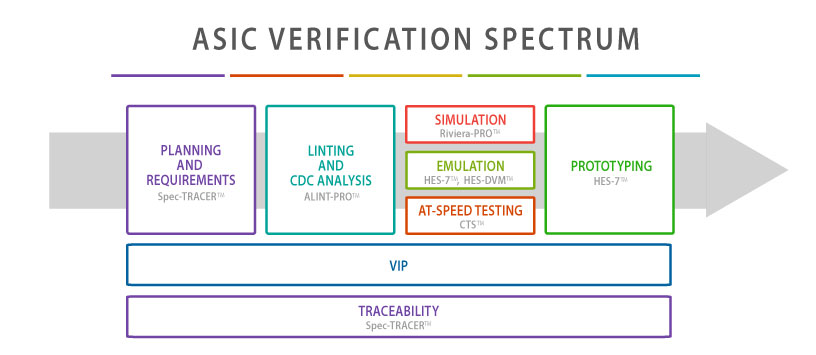

“Verification of complex designs comprised of NoC structures requires a robust chain of verification methodologies such as static linting, high-performance HDL simulation/debugging, and emulation,” said Louie De Luna, Aldec Director of Marketing. “The Verification Spectrum begins as soon as the first lines of HDL code are available, where designers use static linting to catch common bugs and check code sanity. Then HDL simulation using a UVM Verification environment is completed to achieve the highest level of debugging with Structural and Functional Coverage. Finally, to shorten days or weeks of simulation runs, long test sequences of constrained-random testbenches can be accelerated using an emulator. With Aldec’s 35,000+ user community, Aldec is committed to support every stage of this process.”

Visitors to Aldec’s Booth #304 at DVCon Europe will have the opportunity to meet directly with Product Managers who will be on hand to demonstrate an NoC design example, illustrating a seamless verification approach that includes:

1. Design source code linting and analysis with ALINT-PRO™ that provides a comprehensive library of pre-defined checking policies and unique visualization tools to improve design analysis and help understand violations that frequently lead to design bugs. Use of a linting solution within early design stages helps to minimize the number of subsequent synthesis & implementation re-runs, and simplifies code maintenance and re-use by keeping the RTL sources clean.

2. HVL/HDL simulation with Riviera-PRO™ that combines the best-in-class simulation solution for VHDL, SystemVerilog and UVM with powerful debugging tools that includes UVM Toolbox, UVM Graph and Class Viewer. Riviera-PRO has been designed to accompany engineers at every step of design and validation, from golden model through RTL to gate-level netlists and timing simulation.

3. UVM simulation acceleration with HES-DVM™ emulation and prototyping platform based on the largest Xilinx® Virtex-7™ and UltraScale™ FPGAs which connect with Riviera-PRO (or 3rd-party simulators) using Accellera® SCE-MI, the industry standard for simulation and emulation interoperability at the transaction level. Related White Paper: Designing UVM Testbench for Simulation and Emulation of Network-on-Chip Design.

About Aldec

Aldec Inc., headquartered in Henderson, Nevada, is an industry leader in Electronic Design Verification and offers a patented technology suite including: RTL Design, RTL Simulators, Hardware-Assisted Verification, SoC and ASIC Prototyping, Embedded, Design Rule Checking, CDC Verification, IP Cores, Requirements Lifecycle Management, DO-254 Functional Verification and Military/Aerospace solutions. www.aldec.com