TOMSK, Russia, May 23, 2017 - FPGA intellectual property (IP) provider IPrium LLC (www.iprium.com) today announced that it has expanded its family of Super-FEC IP products with a new OTU3 40G I.6 LDPC Codec IP Core for the G.975.1 standard.

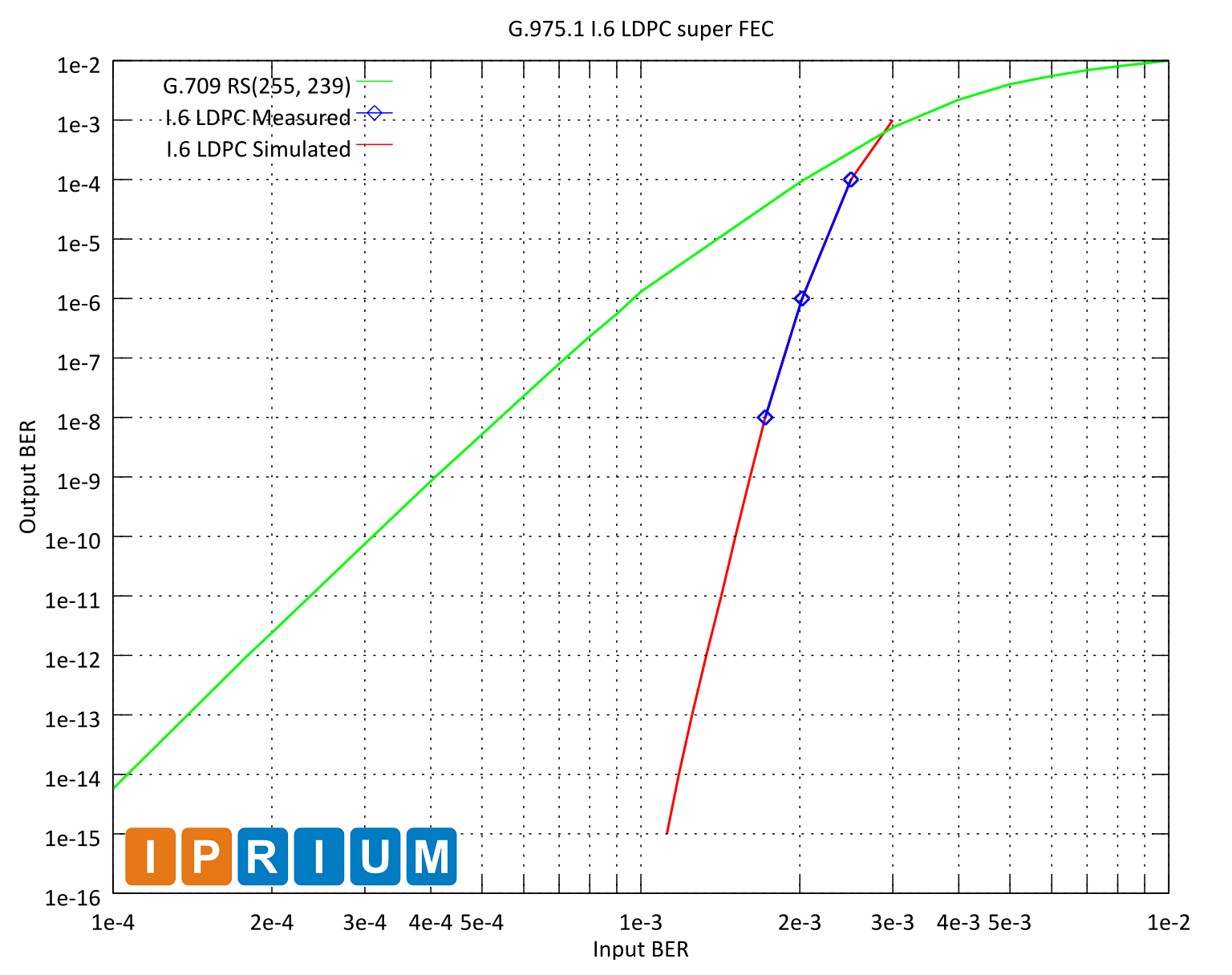

The IP Core is a complete Encoder and Decoder module and is optimized for 40-46 Gbit/s optical communication systems. The redundancy ratio of the super-FEC code is 6.69% and the net coding gain is 8.02 dB for output BER=1e-15.

The 40G I.6 LDPC Codec has been silicon-proven and is compliant with ITU-T G.975.1 Standard (as of 02/2004) "Forward error correction for high bit-rate DWDM submarine systems. Appendix I. Super FEC schemes I.6 LDPC super FEC code".

The IP Core provides turnkey single-chip solution that can be used in low-cost high-throughput applications.

Pricing and Availability

The 40G I.6 LDPC Codec IP Core is available immediately in synthesizable Verilog or optimized netlist format, along with synthesis scripts and simulation test bench with expected results.

For further information, product evaluation, or pricing, please visit the IP Core page:

About IPrium LLC

IPrium Modem IP Cores allow designers of communication equipment to rapidly and cost-effectively develop and verify their systems. IPrium offers FPGA and ASIC IP Cores for high-quality modems to customers worldwide. Visit IPrium at www.iprium.com.