In collaboration with the Centro de Investigación en Computación of the Mexican IPN, Centro Nacional de Microelectrónica of the CSIC and the Universitat Politècnica de Catalunya (UPC).

Lagarto, which is built with TSMC’s 65-nanometer transistors, is the first open source instruction set architecture (ISA) chip developed in Spain, coordinated by the Barcelona Supercomputing Center (BSC). The chip, which has performed better results than expected, is a key step in the center's strategy to become a benchmark in the open source hardware technologies’ field developed in Europe.

Lagarto is an important step in the search of the BSC, led by the center's director, Mateo Valero, to develop European computing technology. This project is based on the premise that the instruction set of the future processors must be open source to ensure transparency and minimize dependence. ISAs constitute the basic set of machine language instructions that a processor can understand and execute and is, therefore, the meeting point between software and hardware. The fact that they are open is intended to circumvent the possibility of chips incorporating backdoors or instructions that may be detrimental to the security or privacy of users.

Open source hardware is a possibility that has emerged in recent years and has the potential to be as disruptive as Linux was once, an open source software paradigm. If Linux managed to lessen the dependence of users in large companies providing software and software applications, it is envisioned that hardware based on ISAs open source can do the same in their own field.

"Lagarto is the first chip with ISA open source developed in Spain and is an embryo of what the BSC intends the European processor to be. The objective of the project was to show that the BSC, which is firmly committed to the development of a processor "made in Europe" is able to create these technologies, and we have succeeded indeed", stresses Mateo Valero.

A large team

The initial design of Lagarto comes from the Centro de Investigación en Computación of the Mexican IPN, a center with which the BSC has maintained a close collaboration for years.

Based on an initial academic design, a team of 30 researchers from the IPN itself, the BSC, the Centro Nacional de Microelectrónica of the CSIC and the Computer Architecture (DAC) and Electronic Engineering Departments of the UPC have worked for nearly two years to manufacture an open ISA RISC-V processor.

The team has been coordinated by Miquel Moretó, head of the Runtime Aware Architectures group of the BSC and researcher Ramón y Cajal of the DAC, and has produced results superior to those expected.

Project Timeline

At the beginning of 2018, the BSC, in collaboration with the Mexican center CIC-IPN, redesigned the initial Lagarto segmented processor, which was based on a MIPS architecture, to convert it into a RISC-V architecture, the open source ISA chosen by the BSC for its chip projects with open architectures, and added to the initial design several modules necessary to turn it into an operational design.

In September of the same year, with the completed and tested design based on simulations, the two centers began a collaboration with the Department of Electronic Engineering at the School of Telecommunications Engineering of Barcelona of the UPC and the Centro Nacional de Microelectrónica of the CSIC to carry out the synthesis part of the project (convert the simulated models into designs based on interconnected hardware components and oriented to their materialization) and their physical design (convert those descriptions to the corresponding geometric drawings of the masks necessary for their manufacture as an integrated circuit or chip) The objective of these phases was to move from digital models or designs to their physical materialization through the corresponding semiconductor technologies, in this case TSMC 65 nanometers.

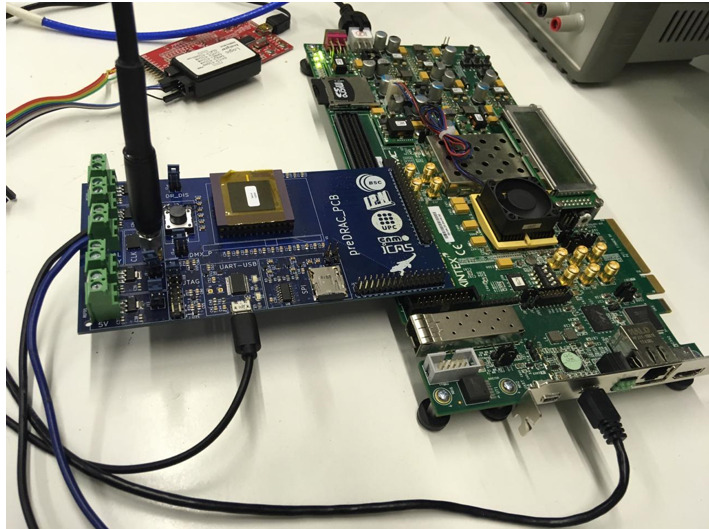

In May 2019, the final design was sent to EUROPRACTICE, a platform created by the European Commission to boost the development of intelligent integrated systems with microelectronic technologies, and this fall 100 "Lagartos" arrived in Barcelona, where the testing process began.

Lagarto is an embryo of what the BSC intends the European processor to be. The BSC plans to create open source chips developed in Europe and suitable for high-performance computing, Internet of Things and other domains, continue with other projects such as the exascale experimental platform associated with MareNostrum 5 (MEEP), which will begin its work in January, the European Laboratory of Open Computing Architectures (LOCA) and the DRAC project, among others.

The participants in this project are very satisfied with the obtained results, as listed below:

Miquel Moretó, project coordinator

“The usual thing is to make a chip several times before it works properly. In the case of Lagarto, not only has it worked at the very first, but it is capable of correctly running numerical calculation applications”.

Marco A. Ramírez, director of the CIC-IPN

“We are very proud of the original design the Mexican IPN has developed together with BSC, CNM and UPC to be manufactured in the TSMC’s 65-nanometer technology. This demonstrates the viability of this project and predicts a very promising future for all the institutions working on it”.

Francesc Moll, UPC professor

"The achievement of this first milestone gives the team confidence to address the following challenges that will allow new features to be incorporated into the next chips to be designed."

Lluís Terés, of the CNM (CSIC) and coordinator of the research network Red-RISCV

"In order for the development of open hardware based on these new RISC-V architectures to be strengthened, it requires the necessary synergies of the prodigious circle "Research-Training-Innovation" as an engine to facilitate a collaborative and joint evolution of the entire ecosystem. Thus, a sustained, sustainable, cooperative and open progress is guaranteed.